Quantum tunneling results in record transistor performance

17 Dec 2011

|

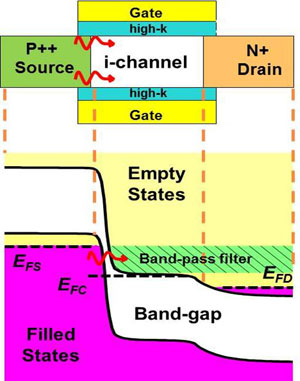

| Schematic of the HTFET showing staggered band alignment (Photo Credit: Penn State) |

Today's digital information processing systems, from data centres to mobile laptops to smart phones, consume and dissipate significant power due to the constant power demand of the billions of transistors packed into the logic circuits on digital electronic devices. In traditional MOSFETs (metal-oxide semiconductor field-effect transistors), the building blocks of today's digital technology, a supply voltage of around one volt is required to gradually turn on the transistor.

The current transistor technology faces inherent limits to reducing the power demand in electronic circuits due to physical laws related to the MOSFET design. Meanwhile, power demand will increase as the size of next generation transistors decreases and more devices are packed onto a computer chip.

In a paper titled ''Demonstration of MOSFET-Like On-Current Performance in Arsenide/Antimonide Tunnel FETs with Staggered Hetero-junctions for 300mV Logic Applications,'' Penn State doctoral candidate Dheeraj Mohata reported a new materials and device architecture that provides power savings and instant transistor on-off capability for future electronics. This was achieved by fabricating a heterojunction field effect tunnel transistor with a 650% increase in drive current.

''This is the first time a tunnelling field effect transistor has had a MOSFET-like On-state current,'' says Mohata's adviser Suman Datta, professor of electrical engineering. ''By choosing two dissimilar semiconductor materials, Indium Gallium Arsenide and Gallium Arsenic Antimonide, and adjusting their composition, Deheeraj was able to engineer Hetero Tunnel FETs with a 7.6x improvement in drive current over the control sample.''

Tunnelling FETs use the quantum mechanical property in which electrons are able to pass through a physical barrier if the barrier is thin enough. By increasing the drive current, the team was able to operate the Tunnel FET at reduced voltage, 300 milliVolt compared to one V, thereby offering considerable power savings.

''If one can pick a proper combination of two different semiconductors and adjust their composition such that their band alignment results in a staggered configuration, it's possible to significantly increase the tunneling rate and enhance the drive current of the Tunnel FET,'' Datta explains.

The Penn State researchers designed and partnered with IQE, who produced the atomically precise multi-layer epiwafers using molecular beam epitaxy on which the transistors are built.

The Penn State team then used advanced nanofabrication techniques to fabricate vertically oriented tunnel FET devices on the epiwafers in the Materials Research Institute's Nanofabrication Facility, whose director, professor of electrical engineering Theresa Mayer, was the co-principal investigator on the project.

Comparing experimental results against the computer models used in the design phase enabled the researchers to verify their device simulations, and determine that Hetero Tunnel FETs would perform in a similar manner in the next generations of semiconductor devices, including future 7nm technology node devices.

''Work has to go on to see if this device can be further scaled to smaller dimensions and integrated on an industrial scale,'' Datta concludes. ''If so, the impact will be significant in terms of low power integrated circuits that can work at 300 millivolts and below. This raises the possibility for self-powered circuits in conjunction with energy harvesting devices for active health monitoring, ambient intelligence, and implantable medical devices where the batteries haven't scaled in step with the devices.''

|

| Suman Datta (left) and Dheeraj Mohata with their HTFET in the Nanoscale Devices and Circuits Lab (Photo Credit: Penn State) |

Other members of the Penn State team along with Mohata, Datta, and Mayer include current and former graduate students, respectively, R Bijesh and Salil Mujumdar in electrical engineering, graduate student Craig Eaton and assistant professor Roman Engel-Herbert in materials science and engineering, and Vijaykrishnan Narayanan, professor of computer engineering.

Their research on Heterojunction Tunnel FETs was funded by Intel Corporation and the Nanoelectronics Research Institute (NRI)-supported Midwest Institute of Nanoelectronic Discovery (MIND). The Materials Research Institute's Nanofabrication Facility is a member of the National Nanofabrication Infrastructure Network (NNIN).

The International Electron Devices Meeting (IEDM) is the world's premier forum for reporting breakthroughs in technology, design, manufacturing, physics, and the modeling of semiconductors and other electronic devices.

.webp)